### EXPANDING STEREO-DISPARITY RANGE IN AN FPGA-SYSTEM WHILE KEEPING RESOURCE UTILISATION LOW

by

Divyang K. Masrani

A thesis submitted in conformity with the requirements for the degree of Master of Applied Science Graduate Department of The Edward S. Rogers Sr. Department of Electrical and Computer Engineering University of Toronto

Copyright © 2006 by Divyang K. Masrani

### Abstract

Expanding Stereo-Disparity Range in an FPGA-system While Keeping Resource Utilisation Low

Divyang K. Masrani

Master of Applied Science

Graduate Department of The Edward S. Rogers Sr. Department of Electrical and Computer Engineering University of Toronto

2006

We present the design and implementation of a Field-Programmable Gate Array (FPGA) based dense stereo depth measurement system that is capable of handling a very large disparity range. The throughput of the system is 60 frames/second on 640 × 240 images. Image rectification and consistency check improve accuracy of the results. The system is based on the Local Weighted Phase-Correlation algorithm [?] which estimates disparity using a multi-scale and multi-orientation approach. Though FPGAs are ideal devices to exploit the inherent parallelism in many computer vision algorithms, their finite resource capacity poses a challenge when adapting a system to deal with large image sizes or disparity ranges. We utilise the temporal information available in a video sequence to design a novel architecture for the correlation unit to achieve correlation over a large range while keeping the resource utilisation very low as compared to a naive approach.

## Dedication

To my family.

## Acknowledgements

I am sincerely grateful to my supervisor, Professor James MacLean, for his invaluable guidance and support that was vital to the success of this thesis.

I would like to express my thanks to my colleagues and friends in the Vision and Image Dynamics Lab and at the University, who were a source of support and encouragement throughout the project. They provided for some very useful discussions both on matters related to the project and to life outside the university.

The University of Toronto, OGS, Micronet R & D and CMC are also acknowledged for their financial and equipment support.

Above all, I am deeply grateful to my family and friends who have made this journey possible for me.

# Contents

|          | Abst     | tract . |                                        | ii  |  |  |  |

|----------|----------|---------|----------------------------------------|-----|--|--|--|

|          | Ack      | nowledg | gements                                | iv  |  |  |  |

|          | List     | of Tab  | les                                    | vi  |  |  |  |

|          | List     | of Figu | ıres                                   | vii |  |  |  |

| 1        | Intr     | oducti  | ion                                    | 1   |  |  |  |

|          | 1.1      | Thesis  | s Objectives and Contribution          | 4   |  |  |  |

| <b>2</b> | Bac      | kgroui  | nd                                     | 7   |  |  |  |

|          | 2.1      | Theor   | etical Basis                           | 7   |  |  |  |

|          |          | 2.1.1   | Stereo Rectification                   | 10  |  |  |  |

|          |          | 2.1.2   | Stereo Matching                        | 12  |  |  |  |

|          |          | 2.1.3   | Locally Weighted Phase Correlation     | 15  |  |  |  |

|          | 2.2      | Recon   | figurable Systems                      | 17  |  |  |  |

|          |          | 2.2.1   | Field Programmable Gate Arrays         | 17  |  |  |  |

|          |          | 2.2.2   | FPGA Design Options                    | 20  |  |  |  |

|          |          | 2.2.3   | Design Approach                        | 21  |  |  |  |

|          |          | 2.2.4   | Transmogrifier-4 Reconfigurable System | 23  |  |  |  |

|          | 2.3      | Previo  | ous Work                               | 24  |  |  |  |

| 3        | Design 2 |         |                                        |     |  |  |  |

|          | 3.1      | Stereo  | Vision System on Transmogrifier-3      | 25  |  |  |  |

|                        | 3.2  | Image            | Rectification Module                                          | 27 |  |

|------------------------|------|------------------|---------------------------------------------------------------|----|--|

|                        | 3.3  | Expan            | ding the Disparity Range                                      | 32 |  |

|                        |      | 3.3.1            | The Tracking Correlation Window                               | 33 |  |

|                        |      | 3.3.2            | System Initialisation                                         | 34 |  |

|                        |      | 3.3.3            | Comparison of the traditional and new architecture $\ldots$ . | 40 |  |

|                        |      | 3.3.4            | Architecture Limitations                                      | 44 |  |

|                        |      | 3.3.5            | Flexibility of Modified Correlation Unit                      | 45 |  |

|                        | 3.4  | Consis           | stency Check Unit                                             | 46 |  |

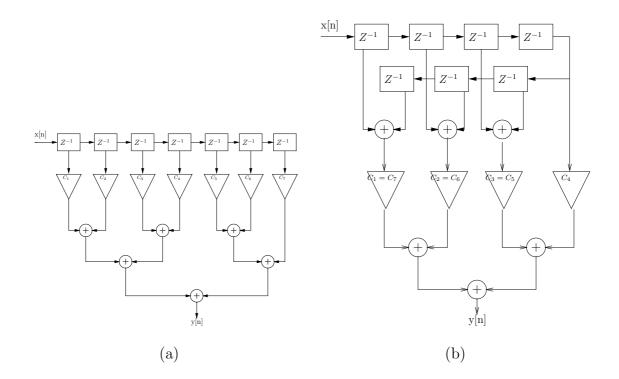

|                        | 3.5  | Stereo           | -Vision system Architecture                                   | 48 |  |

|                        |      | 3.5.1            | Stereo-vision system on Transmogrifier-4                      | 54 |  |

|                        | 3.6  | Summ             | ary                                                           | 56 |  |

| 4                      | Res  | ulte             |                                                               | 58 |  |

| Ŧ                      |      |                  |                                                               |    |  |

| 4.1 System Performance |      | System           | n Performance                                                 | 58 |  |

|                        | 4.2  | System           | n Results                                                     | 60 |  |

|                        |      | 4.2.1            | Image Rectification                                           | 61 |  |

|                        |      | 4.2.2            | Scale and Orientation Decomposition                           | 62 |  |

|                        |      | 4.2.3            | Disparity Results                                             | 62 |  |

|                        |      | 4.2.4            | Consistency Check Results                                     | 66 |  |

|                        |      | 4.2.5            | Analysis of Disparity Results                                 | 68 |  |

|                        | 4.3  | Summ             | ary                                                           | 73 |  |

| <b>5</b>               | Con  | clusio           | ns and Future Work                                            | 74 |  |

|                        | 5.1  | Future           | e Work                                                        | 75 |  |

| A                      | Ster | reo Re           | ctification                                                   | 79 |  |

|                        | A.1  | A.1 Camera model |                                                               |    |  |

|                        | A.2  | Rectifi          | ication                                                       | 80 |  |

|                        |      |                  |                                                               |    |  |

## **B** Simplification of Voting Function

# List of Tables

| 3.1 | Resource usage of modified and old architectures                | 44 |

|-----|-----------------------------------------------------------------|----|

| 4.1 | Comparison of various real-time stereo systems                  | 59 |

| 4.2 | Percentage of accepted and rejected disparities                 | 69 |

| 4.3 | Percentage of error in disparity                                | 72 |

| B.1 | Comparison of basic block requirements for voting function unit | 85 |

# List of Figures

| 2.1  | Triangulation                                                                | 8  |

|------|------------------------------------------------------------------------------|----|

| 2.2  | The epipolar constraint                                                      | 9  |

| 2.3  | Epipolar constraint in parallel camera configuration                         | 10 |

| 2.4  | A simple stereo system                                                       | 11 |

| 2.5  | Stereo rectification                                                         | 12 |

| 2.6  | LUT Architecture of Stratix chip                                             | 18 |

| 2.7  | Stratix features                                                             | 19 |

| 2.8  | Stratix features                                                             | 20 |

| 2.9  | Design Approach                                                              | 22 |

| 2.10 | TM-4 Reconfigurable System                                                   | 23 |

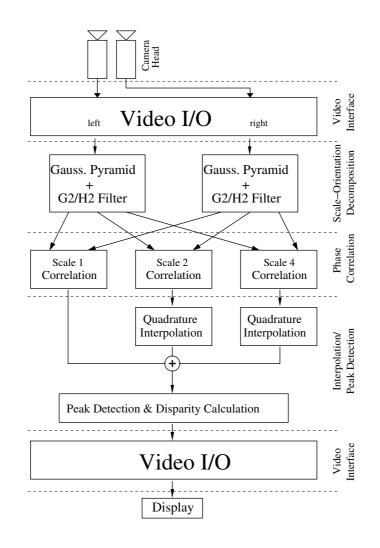

| 3.1  | Stereo-Vision system on TM-3                                                 | 26 |

| 3.2  | Warped image orientation with for various precision of coefficients $\ldots$ | 30 |

| 3.3  | RMS error of warped images with various precisions of coefficients           | 31 |

| 3.4  | Architecture of Image Rectification Unit                                     | 31 |

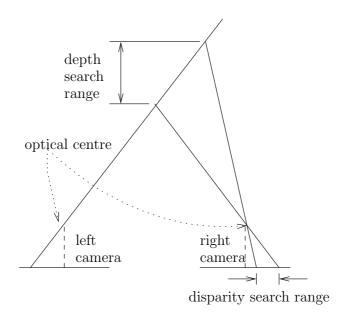

| 3.5  | Relationship between epipolar search band and recovered depth in a scene.    | 32 |

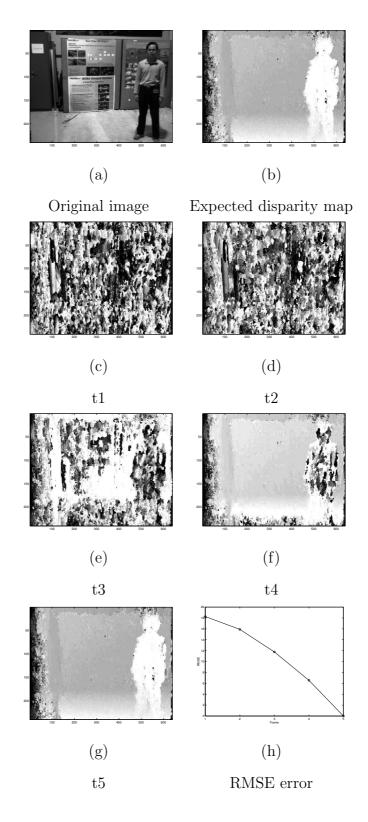

| 3.6  | Initialisation stage of temporal algorithm                                   | 37 |

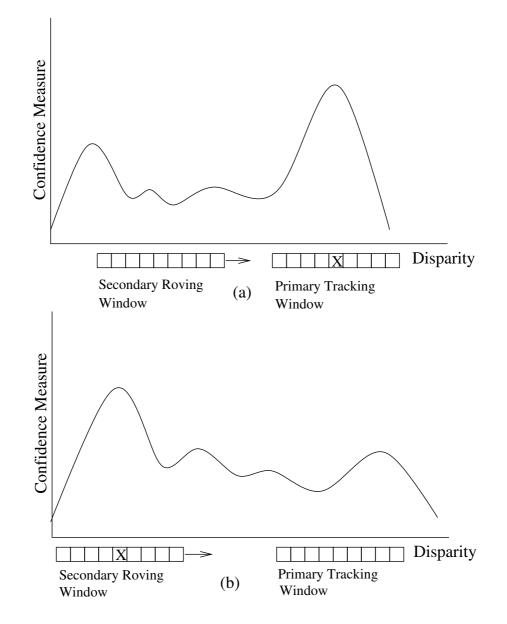

| 3.7  | Primary Tracking and Secondary Correlation Windows                           | 38 |

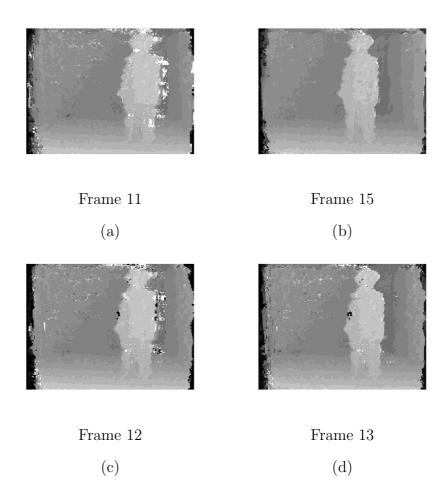

| 3.8  | Trade-off between recovery time and maximum disparity                        | 39 |

| 3.9  | Error correction feature of LWPC                                             | 40 |

| 3.10 | Traditional correlation unit architecture                                    | 41 |

| 3.11 | Novel correlation unit architecture                                                                 | 42 |

|------|-----------------------------------------------------------------------------------------------------|----|

| 3.12 | Difference in disparity between the use of a 1-D and 2-D Gaussian mask .                            | 45 |

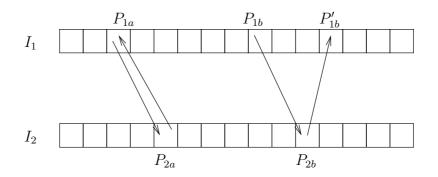

| 3.13 | Consistent vs inconsistent matches $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 47 |

| 3.14 | Architecture of Consistency Check Unit                                                              | 48 |

| 3.15 | High-level architecture of the stereo system                                                        | 50 |

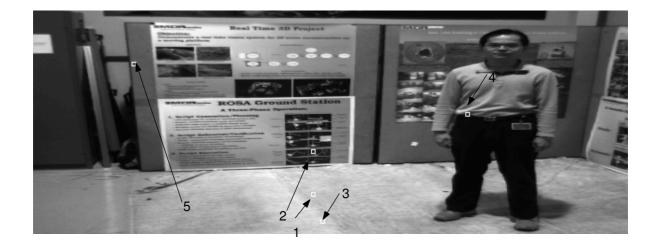

| 3.16 | Stereo rig with NTSC cameras                                                                        | 51 |

| 3.17 | Synchroniser circuit                                                                                | 52 |

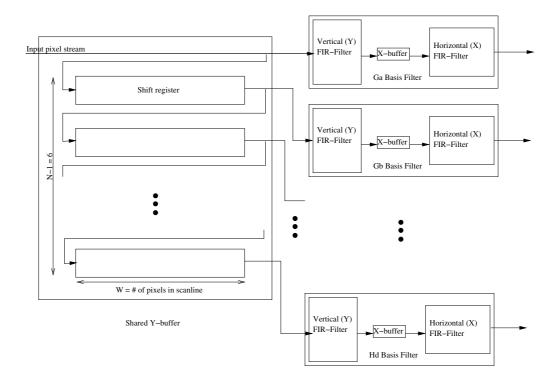

| 3.18 | Architecture of 2-D X-Y separable filters                                                           | 53 |

| 3.19 | FIR filter architecture in hardware                                                                 | 54 |

| 3.20 | Stereo-vision system on TM-4 board                                                                  | 55 |

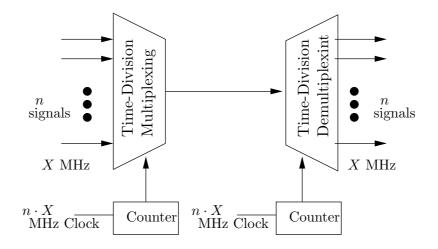

| 3.21 | Data transfer using Time Division Multiplexing                                                      | 56 |

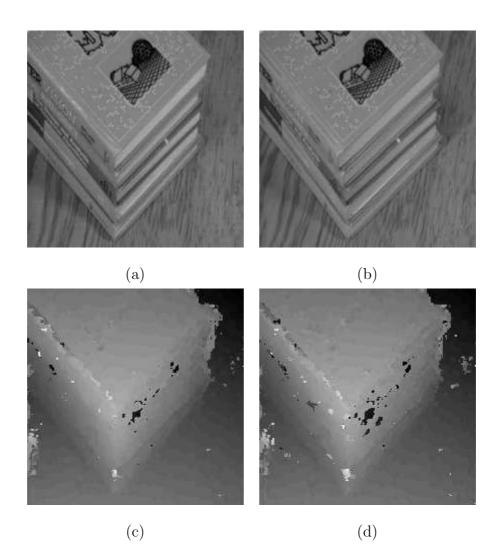

| 4.1  | Image rectification results                                                                         | 61 |

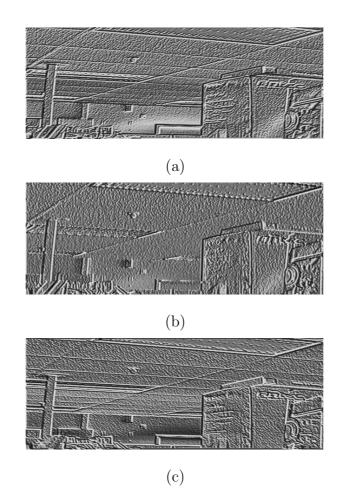

| 4.2  | Scale decomposition results                                                                         | 63 |

| 4.3  | Orientation decomposition results                                                                   | 64 |

| 4.4  | Image sequence from left camera                                                                     | 64 |

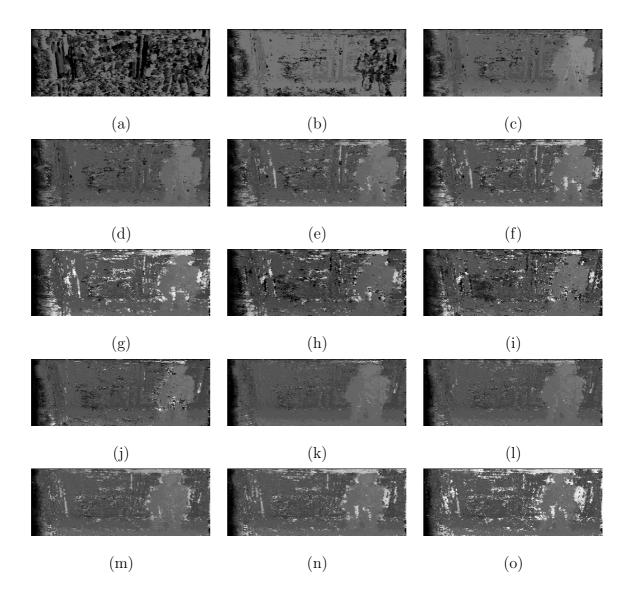

| 4.5  | Disparity map from left-right correlation                                                           | 65 |

| 4.6  | Disparity map from golden version                                                                   | 66 |

| 4.7  | Consistency check results                                                                           | 67 |

| 4.8  | Histogram of disparity difference for frames 4 to 15                                                | 70 |

| 4.9  | Histogram of disparity difference for frames 10 to 12                                               | 71 |

| 4.10 | Blocks used to compare disparity estimates                                                          | 72 |

| 5.1  | Modified buffer to store three rows                                                                 | 77 |

| B.1  | Architecture of original voting function unit                                                       | 83 |

| B.2  | Architecture of modified voting function unit                                                       | 84 |

| B.3  | Effects of modifying voting function on disparity map                                               | 86 |

# Chapter 1

# Introduction

The goal of a *computational vision* system is to automate the task of generating a description of a given scene through an analysis of captured images of the scene. The description of the scene can consist of information such as the location of single or multiple objects in the scene, the identity of objects, or even any actions an object is performing.

The task of building a general purpose computational-vision system is a "grandchallenge" due to the compute-intensive nature of many vision algorithms. However, researchers have been successful in designing algorithms and building systems that deal with some specific tasks of the human vision system. One important feature of the human vision system is its ability to perceive depth of a viewed scene. This ability to perceive depth, known as *stereo vision*, or *stereopsis* is made possible by the difference in viewpoints of the scene when sensed by our left and right eyes. The information about depth in a scene is of great importance because it helps us navigate in a three-dimensional environment and aids us in recognising objects of interest, among other tasks.

In computer based stereo-vision systems, a *stereo-rig* is a pair of cameras placed side-by-side, much like our eyes, to capture the left and right images. The processing required to extract depth information from the image pair may seem second nature when performed by the human brain due to its immense and complex computational capabilities. In a stereo-vision system, this processing is carried out using a computing platform that can be based on software, hardware, or a mixture of the two. The depth information is encoded in the *disparity*, defined as the difference in pixel locations of corresponding points in the image pair. The disparity is inversely proportional to the distance of an object from the cameras, so the disparity increases as objects get closer to the cameras. The estimation of this disparity then becomes the primary task of a stereo-vision system.

In the simplest setup of a stereo-rig, where the optical axes of the two cameras are parallel and the vertical axes are aligned, corresponding pixels lie at the same vertical coordinate in the image pair. The search for the corresponding pixel is therefore limited to the same *scanline* in the image pair, which allows processing of each scanline as they arrive. In the more general case where the cameras are not aligned as described above, the search for corresponding pixel may span across numerous scanlines and this increases the computational load of the system. When the cameras are not in the ideal setup, *Image rectification* of input images can be performed. *rectification* is the process by which the input image pair is warped to resemble the output from an aligned stereo-rig.

Often, when viewing a scene from different viewpoints as in a stereo setup, objects visible in one image may not be visible in the other image. A foreground object hides, or *occludes*, different parts of the background in the left and right views, a phenomenon known as *occlusion*. In addition, the information present at the left edge of the image captured by the left camera is not available in the right image and vice-versa as this part of the scene falls outside the viewing area of the other camera. This further complicates the task of accurate disparity estimation because pixels visible in one image may not have a corresponding match in the other image of the pair.

Many stereo-vision applications require the depth information for every single pixel, which translates to finding a *dense disparity estimate*, the estimation of disparity for every single pixel in the image. Some of the most commonly used cameras today capture images that are  $640 \times 480$  pixels in dimension at a rate of 30 frames per second (fps). To bridge the gap between the desired frame-rate response and the actual performance that general purpose computing platforms can provide, appropriate hardware accelerators need to be used.

Dense stereo-vision algorithms based on a technique called correlation have inherent parallelism which can be exploited to achieve significant improvements in the execution time of the algorithm. Hardware accelerators in the form of Digital Signal Processors (DSPs), reconfigurable devices such as Field Programmable Gate Arrays (FPGAs), and Application Specific Integrated Circuits (ASICs), all provide a viable alternative to take advantage of inherent parallelism as opposed to the use of expensive and large-scale parallel computers for a similar task.

DSPs are commonly used to speed up the computation of many signal and image processing algorithms. Though easy to program, DSPs have a fixed architecture that limits the kind of operations that can be performed. DSPs therefore do not provide a system-on-a-chip solution which is a drawback when space and mobility are a concern. ASICs on the other hand provide the greatest amount of flexibility in designing the architecture but suffer from a long and tedious design process. Furthermore, the high cost of designing and fabricating an ASIC can make it prohibitive to use.

Reconfigurable devices such as FPGAs provide a middle ground. The design process is shorter and cheaper than for an ASIC and they provide much greater flexibility than DSPs making it possible to develop a variety of algorithms from start to end on the FPGA. Another important advantage of FPGAs is that they are reconfigurable, a process that can be completed in a span of milli-seconds, so that the same chip can be used for different algorithms. This makes FPGAs ideal for computer-vision tasks which often require the result from multiple algorithms to accurately make a decision. Take the case of image segmentation. Methods used for image segmentation rely on information such as texture, depth, and colour. No one method will accurately perform segmentation in every scenario, but a combination of information provides the best solution. An FPGA can be easily reconfigured with these different algorithms as needed.

While designing with FPGAs is faster than designing Application Specific ICs (ASICs), it suffers from the problem of fixed resources. In an application based on a serial CPU or DSP, one can typically add memory or disk space to allow the algorithm to handle a larger version of the same problem, for example larger image sizes or increased disparity ranges in the case of stereo. System performance in terms of timing may suffer, but the advantage of such serial implementations is that the new system still runs. In the case of FPGA-based systems, there is a finite amount of logic available, and when this is exhausted the only solution is to add another device or modify the algorithm. Not only is this costly from the design point of view, but may also involve the additional design issue of how to partition the logic algorithm across several devices which is non-trivial. Apart from finding logical partitions in the algorithm, issues with transferring large amounts of data from one FPGA to another in the limited bandwidth between available between FPGAs and also meeting strict timing requirements make this a challenging task. Keeping this in mind, it is important to devise a suitable architecture for the vision system on hand for a successful implementation on FPGAs.

### **1.1** Thesis Objectives and Contribution

Stereo disparity estimation is a prime application for a hardware accelerated computer vision system. Since stereo can provide depth information, it has potential uses in navigation systems, robotics, object recognition and surveillance systems, just to name a few. Due to the computational complexity of many stereo algorithms, a number of attempts have been made to implement such systems using hardware [?, ?, ?, ?], including reconfigurable hardware in the form of FPGAs [?, ?, ?, ?]. One of the more recent attempts at developing a stereo-vision system is described in [?]. The system is based

on the Local Weighted Phase Correlation (LWPC) algorithm [?] and is implemented on the Transmogrifier-3 reconfigurable computing platform [?]. Though the system provides dense disparity estimates at 30 fps, it has several major limitations. The amount of logic resources required by the system is directly proportional to the largest disparity that the system can support. The system is capable of handling a maximum disparity of only 20 pixels, which for the particular set-up of the system does not generate accurate depth information for objects closer than 2 meters from the camera. This is a severe hinderance to the use of the system in many applications such as autonomous navigation. Furthermore, the system does not attempt to rectify the input images, which affects the accuracy of the results, and it supports an image size of only  $256 \times 360$  pixels.

In this work, we address the specific limitations of the previous system mentioned above. The goal of this work is to develop a versatile real-time stereo-vision platform with various salient features; capability to handle very large disparities, improved accuracy by pre-processing (input image rectification), and the ability to handle larger images. The highlight of the work is the development of a novel architecture that can handle the correspondence task for scenes with very large disparities, but without increased resource usage on the FPGA, as compared to [?]. The key to achieving large disparity correspondence matches is the use of shiftable correlation windows that track the disparity estimate for each pixel over time, as well as secondary roving correlation windows that explore the correlation surface outside the range of the shiftable tracking window in order to detect new matches when the tracking window is centred on an incorrect match. In our work, the shiftable tracking window is termed the *Primary Tracking Window (PTW)* and the window that performs roving correlation as the *Secondary Roving Window (SRW)*. The basic assumption in our approach is that, in most cases, disparity values do not change radically between frames, thus allowing some of the computation to be spread over time.

The thesis is organised as follows. Chapter 2 describes the relevant background in stereo-vision and reconfigurable computing systems. In Chapter 3 we present the main fo-

cus of this thesis; development of hardware architectures for image rectification, expanded disparity range support, and consistency check of stereo disparity estimates. Chapter 4 compares the stereo-system in this work with others in the literature and disparity results from the system are also presented. We conclude in Chapter 5 with a summary and a discussion of possible directions for future work.

# Chapter 2

# Background

In Chapter 1 we established the focus of this work; developing a novel architecture for a stereo-vision system that is capable of supporting very large disparity range without a corresponding increase in the logic resource usage. In order to achieve this with the limited resources offered by FPGAs, an understanding of the various stereo matching algorithms and knowledge of the hardware technology that will be used is required.

This chapter first provides an overview of binocular stereo vision, the options available for stereo-matching and a justification for the selected technique for this work in Section 2.1. Section 2.2 gives an introduction to FPGA technology and the reconfigurable computing platform used in this work. Finally, in Section 2.3, a brief review of previous work in hardware-based computer vision and image processing is presented.

### 2.1 Theoretical Basis

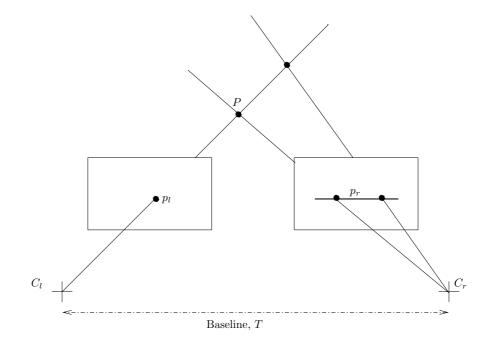

Stereopsis is the process in visual perception leading to perception of depth or distance of objects. Depth from stereopsis, in particular *binocular stereopsis*, arises from the difference in the viewpoints of the two cameras that view the scene. This process is known as *triangulation* and is illustrated in Figure 2.1. In the case of binocular stereo, a *scene point* (point in the 3-D world space) is projected on the two image planes of the camera pair; these projected points are knows as image points. Given the centre of projection of the two cameras, two rays are formed that go through the the centre of projection of each camera and image point of the respective camera. The location of the scene point is at the intersection of the two rays.

Figure 2.1: Given the projections of a scene point in both the left and right image, the three-dimensional location of the scene point can be determined by triangulation.

From a computational standpoint, a stereo system must solve two problems [?]. The key to performing triangulation is to first establish point correspondences, or in other words, for each point in one image, find the point in the other image that is a projection of the same scene point if it exists. This task of solving for stereo correspondence is the first problem of stereo and because it involves searching for matching points in the binocular image pair, it is often termed *stereo matching*. The search for corresponding points need only be performed along a one-dimensional line rather than a two-dimensional search area if the stereo images have been rectified. The surety of finding the corresponding point along the line is guaranteed by the *epipolar constraint* which says that given an image point  $p_l$ , its corresponding point  $p_r$  in the other other image is constrained to lie

along the *epipolar line* which is formed by the intersection of the plane formed by  $P, C_l$ , and  $C_r$  and the image plane, where P is the scene point and  $C_l$  and  $C_r$  are the camera centres of the left and right cameras as illustrated in Figure 2.2.

Figure 2.2: The epipolar constraint guarantees the location of a corresponding image point along the epipolar line in the image pair.

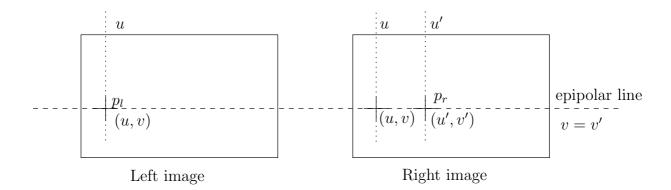

The simplest binocular stereo system is one whose optical axes are parallel, vertical axes are aligned and with each camera having identical focal lengths. In such a configuration, the epipolar lines coincide with the *scanlines* of the images, thus simplifying the search. For a scene point P having corresponding image points  $p_l$  at (u, v) and  $p_r$  at (u', v') one in each image of the pair, the vertical positions are the same, that is, v = v'as shown in Figure 2.3. The difference in the horizontal locations of the corresponding image points

$$d = u' - u \tag{2.1}$$

is termed the *binocular disparity*, or simply the *disparity*. The horizontal locations, u and u' are measured relative to the the respective image centres.

Figure 2.3: Epipolar constraint in parallel camera configuration.  $p_l$  and  $p_r$  are point correspondences of the same scene point.  $p_l$  and  $p_r$  lie along the same scanline (same vertical position).

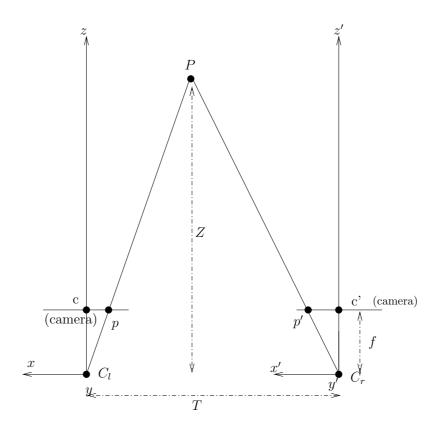

Given the camera calibration parameters, the depth of a point P in 3-D space can be obtained using similar triangles as shown in Figure 2.4. The depth z is calculation using the equation

$$z = f \frac{T}{d} \tag{2.2}$$

where f is the focal length of the camera, and  $T = ||C_l - C_r||$  is the baseline of the stereo system. The computation of this depth is the second problem of stereo, also known as the problem of *reconstruction*. This is a more challenging problem when the cameras are in a general position.

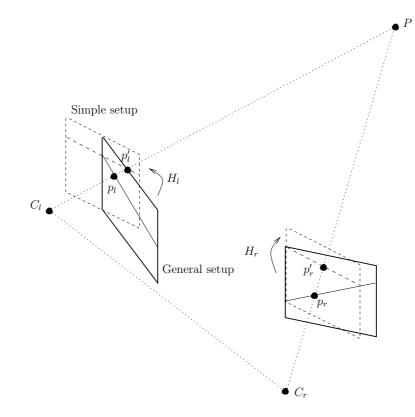

#### 2.1.1 Stereo Rectification

The problem of finding correspondence in an image pair taken from cameras in a general position can be simplified by rectifying the image pair before proceeding to find the matches. Rectification is the process by which the two images taken from cameras in a general position are reprojected onto a common image plane that is parallel to the baseline of the stereo-rig. This is illustrated in Figure 2.5. The rectified images can be thought of as acquired by a new stereo-rig, obtained by rotating the original cameras around their optical centres.

Figure 2.4: Given the stereo rig calibration parameters and the disparity measure, the depth, Z, of a scene point, P, can be determined. T is the baseline of the stereo rig and f is the focal length of the cameras.

Mathematically, the reprojection can be described by a  $3 \times 3$  projection or *homography* matrix **H**. The matrix **H** represents the transformation of coordinates from the original image to the reprojected image as follows:

$$\begin{bmatrix} x'\\y'\\z' \end{bmatrix} = \mathbf{H} \begin{bmatrix} x\\y\\1 \end{bmatrix}$$

(2.3)

The stereo pair can then be rectified by applying two appropriate homographies  $\mathbf{H}_l$ and  $\mathbf{H}_r$  to the two images.  $\mathbf{H}_l$  and  $\mathbf{H}_r$  are computed from the position and orientation of the two cameras given that the stereo-rig has been calibrated and its intrinsic and extrinsic parameters are known. Further information on this process is given in Appendix A.

Figure 2.5: The simple stereo geometry can be derived from a general setup by reprojecting the two images onto a plane parallel to the baseline.

The actual rectification is performed using backward mapping by re-sampling the original images. For each pixel (x', y') in the rectified image, the corresponding pixel (x, y) in the original image is computed using  $\mathbf{H}^{-1}$ . This backward mapping produces real-valued coordinates in the original image so the intensity value of each pixel in the rectified image must be interpolated from pixels in this neighbourhood. One method of obtaining the intensity values for the rectified image is through *bilinear interpolation*, which computes the intensity value from a neighbourhood of four pixels.

#### 2.1.2 Stereo Matching

According to [?], stereo matching algorithms, in general, can be broken down into the following four steps:

- 1. matching cost computation: some common ones include squared intensity differences (SD), absolute intensity differences (AD), normalised cross-correlation, and binary matching costs based on features such as edges. The Locally Weighted Phase Correlation (LWPC) algorithm used in this work is similar to normalised cross-correlation;

- cost (support) aggregation: the summing or averaging of the matching cost over a support region, which is normally in the neighbourhood of the pixel;

- 3. disparity computation / optimisation: refers to selecting the best disparity estimate based on the aggregated cost and in some cases the subsequent improvement of the estimate with respect to some criteria; and

- 4. disparity refinement: in certain situations, there might be a need to obtain disparity estimate at sub-pixel accuracy using methods such as iterative gradient descent or fitting a curve to the matching costs at discrete disparity levels.

Specific algorithms may alter the sequence of the steps, combine steps, or skip some of the computation altogether.

Stereo matching algorithms can be classed into two categories; one that generate sparse disparity maps and another that generate dense disparity maps. Algorithms that generate sparse disparity maps rely on features such as edges or corners for matching and this matching is commonly known as *feature based matching*. A detailed survey of many sparse algorithms is available in [?] and will not be discussed here. Many vision applications require dense disparity estimates and we focus on this class of algorithms in this work. Dense disparity estimates can be generated from a sparse map by interpolation, but this approach requires several assumptions about the scene geometry, and is burdened with difficulties. More important is the class of algorithms that generate dense disparity maps directly without the need for interpolation.

Stereo matching algorithms that generate dense disparity maps can further be classified into *local* (window-based) or *global* depending on the optimization performed in *Step 3* of the above described steps. The computational emphasis of local methods is put on matching cost computation and on the cost aggregation steps. The optimisation is a local "winner-take-all" optimization at each pixel [?] limited to the extent of the correlation window. Despite the drawback of only local optimization, the fact that these algorithms use a *local support* area, commonly known as the *correlation window* means they exhibit regular computational structures that allow for efficient parallel implementation on hardware such as DSPs, ASICs, and FPGAs. A number of local algorithms have been implemented on various types of hardware and a survey of these can be found in Section 2.3.

The computational focus of global algorithms, on the other hand, is on the optimization step. These algorithms seek to optimise a global energy function consisting of a "data term" and a "smoothness term",

$$E(d) = E_{data}(d) + \lambda E_{smooth}(d).$$

(2.4)

The data term,  $E_{data}(d)$ , gives a measure of the the likeness between the input image pair and the disparity function d. The smoothness assumptions made by the algorithm in the viewed scene are encoded in the smoothness term,  $E_{smooth}(d)$ . Global algorithms use several different methods to achieve minimisation of the energy function. These include simulated annealing [?], relaxation labeling [?] and non-linear diffusion of support [?]. More recently, algorithms based on graph-cuts [?] have been developed, and represent the state of the art for accuracy.

It is worth noting that though global algorithms provide more accurate dense disparity measurements compared to local algorithms, they have much higher computational costs, where the 2-D optimisation of (global equation) is often NP-hard [?], that render this class of algorithms unsuited to frame-rate applications. With current hardware technology, it is a challenge to even implement local algorithms that use complex matching techniques. It is the focus of this work to first design an efficient architecture for hardware implementation of local algorithms.

#### 2.1.3 Locally Weighted Phase Correlation

The system implemented in this work is based on the "Local Weighted Phase Correlation" (LWPC) algorithm [?], which estimates disparity at a set of pre-shifts using a multi-scale, multi-orientation approach. A version of this algorithm was implemented in [?] but that system is limited to handling a maximum disparity of 20 pixels due to resource limitations on the FPGA, and has no input image rectification.

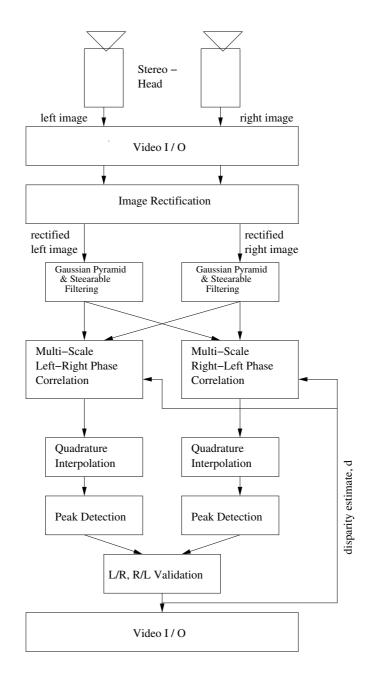

The LWPC algorithm has four major steps. A three-scale Gaussian pyramid is first created from the original images, sub-sampled at each level by a factor of two horizontally and vertically. Each level of the pyramid is decomposed into three orientations by applying quadrature-pair G2-H2 filters, tuned to orientations  $0^{\circ}$ ,  $+45^{\circ}$ ,  $and - 45^{\circ}$  [?]. G2 is the second derivative,  $\frac{\delta^2}{\delta x^2}G(x, y; \mu, \sigma)$ , of a Gaussian and H2 is the Hilbert transform of G2. G2-H2 filters of any orientation can be synthesised as linear combination of a set of "basis filters"; three basis filters for G2 and four for H2 are needed.

Correlation is then performed on each filtered pair of images at a set of pre-shifts. The correlation scores for a pair of images at each of these pre-shifts is collectively known as the *confidence measure* function. The confidence measure is then summed across all the scales and orientations so that spurious peaks are attenuated while the true peaks are re-inforced. The correlation results for the coarser scales must be interpolated to have the same resolution as the original scale before performing the summation. Finally, the peak must be located in the combined confidence measure function for each pixel. This peak is the estimate of the disparity for the particular pixel. The algorithm can be summarised as follows:

1. Create a Gaussian pyramid with total number of scales S for both left and right images. Apply spatially-oriented quadrature-pair filters [?] to each scale of the pyramid at F orientations. If  $K_j(x)$  is the filter impulse response of the *j*th orientation, then we can write the complex-valued output of the convolution of  $K_j(x)$ with each scale of the left and right images,  $I_l(x)$  and  $I_r(x)$ , as

$$O_l(x) = \rho_l(x)e^{i\phi_l(x)} = K_j(x) \otimes I_l(x) \quad and$$

$$O_r(x) = \rho_r(x)e^{i\phi_r(x)} = K_j(x) \otimes I_r(x)$$

in polar representation, where  $\rho(x) = |O(x)|$  is the amplitude and  $\phi(x) = \arg[O(x)]$  is the phase of the complex response.

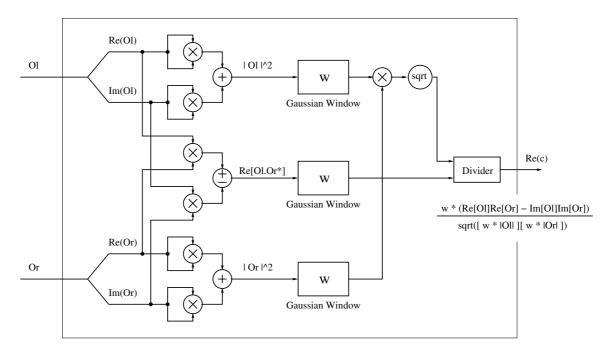

2. For each scale and orientation, compute local voting functions  $C_{j,s}(x,\tau)$  in a window centred at  $\tau$  as

$$C_{j,s}(x,\tau) = \frac{W(x) \otimes [O_l(x)O_r^*(x+\tau)]}{\sqrt{W(x) \otimes |O_l(x)|^2}\sqrt{W(x) \otimes |O_r(x)|^2}},$$

(2.5)

where W(x) is a smoothing, localized window and  $\tau$  is the pre-shift of the right filter output.

3. Combine the voting functions  $C_{j,s}(x,\tau)$  over all orientations,  $1 \le j \le F$ , and scales,  $1 \le s \le S$ , where F is the total number of orientations, to get the cumulative voting function

$$V(x,\tau) = \sum_{j,s} C_{j,s}(x,\tau) \; .$$

4. For each image position x, find the  $\tau$  value corresponding to the peak in the real part of  $V(x, \tau)$  as an estimate for the true disparity.

The reason for basing our work on this algorithm is two-fold. First, the LWPC algorithm is one of the more complex and recent local algorithms. The results obtained using this algorithm have greater accuracy than simpler local algorithms such as ones based on sum-of-squared-differences (SSD) [?, ?, ?] or sum-of-absolute-differences (SAD)

[?]. The second is that a previous implementation [?] of this algorithm exists, but is limited to a maximum disparity of 20 pixels, which in the set-up of that system means any objects closer than 2 meters from the camera will not have accurate disparity estimates. It is our hope that by creating a hardware stereo system based on this algorithm without significant loss of features, as compared to its software version, and at the same time providing frame-rate performance we can encourage computer scientists who develop stereo, and in general, vision algorithms, to steer their work towards hardware based algorithms. At the same time, we hope that we can also encourage hardware designers to break from a traditional approach of designing some common arithmetic components so that more of the complex algorithms have implementations on hardware.

### 2.2 Reconfigurable Systems

A reconfigurable system is a computing system that can be reprogrammed to perform many different tasks, often to support future upgrades and enhancements. Reconfigurable systems have at their core single or multiple interconnected FPGAs that act as the main processing unit of the system. FPGAs, by nature, are reconfigurable and thus provide this functionality to the system. In addition to the FPGA(s), a reconfigurable system may also provide various means of supplying input to the system, such as audio or video signals, and also the ability to capture the results of the system. The communication with other systems and peripherals are through interfaces such as Peripheral Component Interconnect (PCI) bus, Universal Serial Bus (USB), or even network-based.

#### 2.2.1 Field Programmable Gate Arrays

An FPGA is an array of logic elements whose behaviour can be programmed by the end-user to perform a wide variety of logical functions, and which can be dynamically reconfigured as requirements change. FPGAs generally consist of four major components: 1) Logic blocks/elements (LB/LE); 2) I/O blocks; 3) Logic interconnect; and 4) dedicated hardware circuitry. The logic blocks of an FPGA can be configured to implement basic combinatorial logic (AND, OR, NOR, etc gates) or more complex sequential logic functions such as a microprocessor. The logic interconnect in an FPGA consists of wire segments of varying lengths which can be interconnected via electrically programmable switches. The density of logic blocks used in an FPGA depends on the length and number of wire segments used for routing.

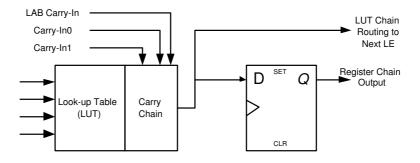

The Altera Stratix S80 device used in this work contains a two-dimensional rowand column-based architecture to implement custom logic. The smallest unit of logic in the Stratix device is called a Logic Element (LE). Each LE contains a four-input LUT, which is a function generator that can implement any binary-valued function of four binary variables. In addition, each LE contains a programmable register and carry chain with carry select capability to facilitate fast implementation of arithmetic components. The architecture of the Stratix LE is shown in Figure 2.6. A set of 10 LEs make up a Logic Array Block (LAB) [?].

Figure 2.6: Simplified LUT architecture of Stratix chip.

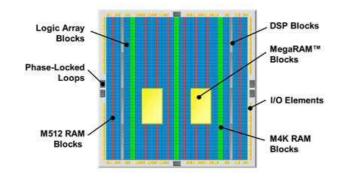

Most modern FPGAs also have various dedicated circuitry in addition to the programmable logic. These come in the form of high-speed and high-bandwidth embedded memory, dedicated DSP blocks, Phase-Locked Loops (PLLs) for generating multiple clocks, and even general purpose processors. The FPGA we are using in our system, the Altera Stratix S80, comes with three different memory block sizes; 512 bits, 4 Kbits, and 512 Kbits for a maximum of 7 Mbits of embedded memory and 22 DSP blocks consisting of multipliers, adders, subtractors, accumulators, and pipeline registers. Figure 2.7 shows an overview of the Altera Stratix S80 chip [?].

Figure 2.7: Advanced features of the Altera Stratix FPGA [?].

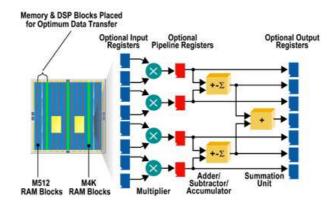

The combination of memory and DSP blocks make the Stratix family of FPGAs ideal for image processing applications as they can efficiently implement many common image processing tasks such as finite impulse response (FIR) filters, discrete cosine transform (DCT), colour space conversion (CSC), and MPEG-related operations among others. Each DSP block, illustrated in Figure 2.8, is optimised to interface with the specialised memory structures in Stratix devices for memory-intensive and high-precision DSP applications. Each DSP block can implement four  $18 \times 18$ -bit signed or unsigned multiplications using dedicated multiplier circuitry. The blocks can also be configured to support eight  $9 \times 9$ -bit multiplication or one  $36 \times 36$ -bit multiplication. In addition, the adder/subtractor/accumulator unit can switch between adder and subtractor functionality, acting as a 9-bit, 18-bit, or a 36-bit unit as necessary. In the accumulator mode, the unit acts as a 52-bit accumulator that can be used to implement operations such as convolutions.

Figure 2.8: DSP Block architecture of Altera Stratix S80 FPGA [?].

#### 2.2.2 FPGA Design Options

FPGA designers have several options for implementing algorithms on the device. The circuitry can be designed by connecting logic gates to generate the desired output, a technique known as *gate-level design*. Gate-level designs result in optimised designs, but the learning curve is considered prohibitory for most engineers, and these designs also suffer from portability issues across FPGA architectures. A more common approach is to design at a higher level using Hardware Description Languages (HDLs). HDLs can efficiently describe the structure and behaviour of digital logic designs for creating ASICs or implementation on FPGAs.

HDLs provide support for describing concurrent event to take advantage of FPGAs' inherent ability to perform multiple operations concurrently. This feature differentiates HDLs from other high-level languages which are primarily intended for software design. HDLs also support inclusion of technology-specific modules, which come in the form of *cores* from FPGA or third-party vendors, for most efficient synthesis to FPGAs. IP (intellectual property) cores are generally parameterisable to suit the user's design and are often designed to provide optimised performance on a particular device or architecture. These cores allow IP to be easily distributed and help in speeding-up the design process.

A number of HDLs currently exist, some of which are proprietary, but two of the most widely used are Verilog HDL, or simply Verilog, and VHSIC (Very High Speed Integrated Circuit) HDL, or simply VHDL. Verilog, a former proprietary language, was originally intended as a simulation language. It has since been updated to be used in synthesis of hardware designs and made into an open standard. VHDL, an open IEEE standard, first appeared in 1987 as IEEE standard 1076-87. VHDL is intended to support the design, verification, synthesis, and testing of hardware designs. A second update, IEEE 1076-93, came out in 1993, and it is currently being considered for a third update. The third update has a number of features specifically suited for implementation of arithmetic algorithms. These include explicit support for variable bit-width floating and fixed point operations, which helps a designer manage these operations in the design better.

The choice of which language to use is arbitrary and depends solely on the designer's familiarity with the language. Geographically, Verilog is more popular on the west-coast of North America, whereas VHDL is the preferred language on the east-coast of North America and in Europe. The language chosen in this work is VHDL and the design is fully compliant with the IEEE standard for VHDL.

#### 2.2.3 Design Approach

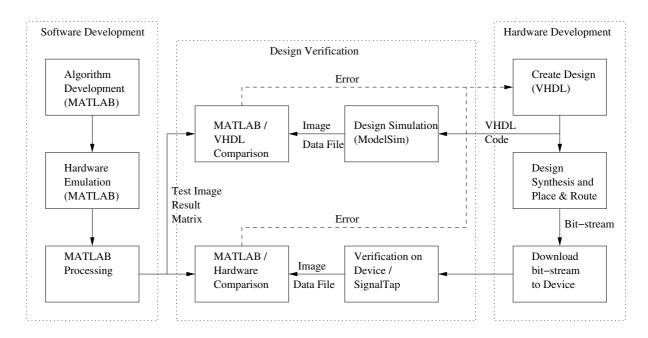

A successful large-scale hardware design requires extensive simulation and verification before a designer can validate the circuit. Designing arithmetic components in hardware often requires that the data be converted to fixed-point format because a floating-point version of the algorithm may not fit on the device. Implementation of floating-point arithmetic on hardware takes up a lot more logic resources than fixed-point operations. However, there is a trade-off between the accuracy of the system and hardware resource usage: greater accuracy requires larger bit representation and therefore more logic resources on the device. In addition, the concurrent nature of hardware design means that the designer must also make sure that the data-flow in a pipelined design is synchronised with the clock-cycle it is intended for. This means that validation must be performed both at bit-true and cycle-true levels. MATLAB was used extensively to facilitate the smooth flow of design and verification of bit-true results. Modifications and extensions to the LWPC algorithm were tested in MATLAB first because it is optimised for matrix operations and provides a platform for a fast implementation. The design approach is shown in Figure 2.9. The figure shows the interaction between the hardware and software phases of the design process. The software phase is on the left side and the hardware phase is on the right side of the diagram. The verification and validation phases are shown in the middle of the diagram.

Figure 2.9: Hardware design approach taken in this work.

Once a satisfactory algorithm was developed, a "hardware emulation" version of the algorithm was coded in MATLAB to produce bit-true results for all components along the data-path. While a matrix-manipulation software program and a hardware implementation are fundamentally different, they should produce the exact same results, provided that care is taken in the hardware design. After completing the emulation version of the algorithm in MATLAB, the hardware design was created component by component. Each component is tested for functionality and cycle-true results using the ModelSim simulator tool. Bit-true results are checked by importing the results from ModelSim into MATLAB and comparing with the results generated from the emulation version. When all components required for a module have been completed, the module is synthesised and a bit-stream is generated. The bit-stream is then downloaded onto the FPGA and the design is verified by providing it with the same input image pairs that were used for the emulation and ModelSim simulation versions. Any errors encountered in the simulation stage were debugged by analysing the signal waveform in ModelSim. Similarly, discrepancies found in the hardware were debugged using the SignalTap on-chip logic-analyser from Altera Corporation. The design was created and verified module by module, which were then all connected to create the complete system.

#### 2.2.4 Transmogrifier-4 Reconfigurable System

The Transmogrifier-4 [?] is a general-purpose reconfigurable prototype board containing four Altera Stratix S80 FPGAs. The board has specific features to support image processing and computational vision algorithms; these include dual-channel NTSC and FireWire camera interfaces, video encoder/decoder chip, and 2GB of DDR RAM connected to each FPGA. Each FPGA is also connected to the other three FPGAs and an interface is provided to communicate with the board over a network. This can be used to send control signal or for debugging. The board is shown in Figure 2.10.

Figure 2.10: Transmogrifier-4 reconfigurable computing board.

### 2.3 Previous Work

A variety of reconfigurable stereo machines have been reported [?, ?, ?, ?, ?]. The PARTS reconfigurable computer [?] consists of a 4 × 4 array of mesh-connected FPGAs with a maximum total number of about 35,000 4-input LUTs. A stereo system was developed on PARTS hardware using the census transform, which mainly consists of bit-wise comparisons and additions [?]. Kanade *et al.*[?] describe a hybrid system using C40 digital signal processors together with programmable logic devices (PLDs, similar to FPGAs) mounted on boards in a VME-bus backplane. The system, which the authors do not claim to be reconfigurable, implements a sum-of-absolute-differences along predetermined epipolar geometry to generate 5-bit disparity estimates at frame-rate.

In Faugeras *et al.*[?], a  $4 \times 4$  matrix of small FPGAs is used to perform the crosscorrelation of two  $256 \times 256$  images in 140 ms. In Hou *et al.*[?], a combination of FPGA and Digital Signal Processors (DSPs) is used to perform edge-based stereo vision. Their approach uses FPGAs to perform low level tasks like edge detection and uses DSPs for higher level integration tasks. In [?] a development system based on four Xilinx XCV2000E devices is used to implement a dense, multi-scale, multi-orientation, phasecorrelation based stereo system that runs at 30 frames/second (fps).

It is worth noting that not all previous hardware approaches have been based on reconfigurable devices. In [?], a DSP-based stereo system performing rectification and area correlation, called the SRI Small Vision Module, is described. ASIC-based designs are reported in [?, ?, ?] and in [?] commodity graphics hardware is used.

# Chapter 3

# Design

In this chapter we first analyse a previous implementation of the LWPC based stereo algorithm to point out the shortcomings of the system. We then describe the design of pre- and post-processing modules in Section 3.2 and Section 3.4 respectively that improve the general accuracy of a stereo algorithm. The highlight of this work is the development of a novel architecture for performing the phase-based correlation which can support a very large disparity range without a corresponding increase in the logic resource requirements as described in Section 3.3. Finally, we show an architecture of a stereo-vision system that incorporates these modifications in Section 3.5.

### 3.1 Stereo Vision System on Transmogrifier-3

The previous stereo system based on the LWPC algorithm was implemented on the Transmogrifier-3 board. The TM-3 board has four Xilinx Virtex 2000E FPGAs. The system was a straight forward implementation of the LWPC algorithm described in Section 2.1.3. A high-level architecture of this system is shown in Figure 3.1.

Two key steps taken to successfully implement the algorithm on the TM-3 board were:

Figure 3.1: High-level architecture of LWPC based stereo-vision system on the TM-3 board.

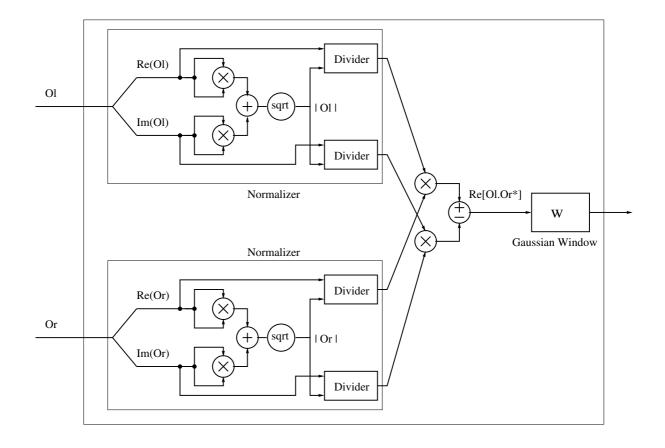

- 1. Modification of the voting function (Step 2 of the LWPC algorithm) to share the normalisation operation and Gaussian filtering for all the pre-shifts  $\tau$ . This reduces the number of multiplication, division, and addition operations by 65% so that the algorithm can be implemented in the FPGAs. A detailed look at this modification and its effects is given in Appendix B.

- 2. Conversion of the computation from floating-point to fixed-point.

The above-mentioned modifications are retained in the work. Even with these modifications, the previous system supported a disparity range of only 20 pixels. Moreover, the system was limited to using two orientations instead of the suggested three in [?]. It is important to note that the LWPC algorithm as described in [?] and its previous hardware implementation [?] compute the disparity of each frame from scratch at every frame. No attempt is made to use the fact that in most situations, the disparity of a pixel will not change drastically from one frame to the next when an image sequence is being captured at 30 frames per second. In this work, we successfully use this information and develop an architecture that is capable of handling very large disparities in the limited resources on the FPGA which we describe in Section 3.3. Section 3.2 describes the design of an image rectification unit which improves the accuracy of the disparity results, and Section 3.4 discusses the design of a post-processing unit to perform a consistency check in the disparity map.

# 3.2 Image Rectification Module

Rectification of an image requires the synthesis of a new image through warping of the original image. The theory of image rectification is described previously in Section 2.1.1. In practice, image rectification is achieved through an *inverse mapping* strategy—each pair of integer pixel coordinates in the rectified image is mapped to a pair of coordinates, not necessarily integer, in the original image. The pixel value for the warped image can be found through bilinear interpolation of the pixel values in the neighbourhood of the mapped coordinates.

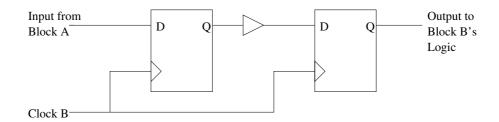

There are two main issues to be aware of when implementing image rectification in hardware. First, since this is an inverse mapping process, we do not have prior information on what exact input is required at each time instance. This means some sort of buffering of the input image is required. In addition, bilinear interpolation requires four input pixels for each output pixel, whereas only one pixel can typically be read out at a time from the buffer. In order to keep up with the rate of incoming pixels one solution would be to store four copies of the incoming pixel stream in separate buffers. This allows all four pixels, one from each of the buffers, to be read at the same time. The incoming pixel rate for our system is about 13.5 MHz which is significantly lower than the full potential of the Stratix S80 FPGA. This gives us another option to achieve real-time performance; by designing a *multi-clock* system. In a multi-clock design, each hardware module is clocked by one of the two or more clocks used in the system which makes it possible to achieve a high-performance design. In this work, the image rectification unit is designed to run on a clock that is set to at least four times the frequency of the camera clock, so that the four pixels needed for bilinear interpolation can be read and processed in the time it takes for a single new pixel to arrive from the camera.

The second issue is efficient implementation of the inverse warping operation to compute the source pixel coordinate in the original image. The inverse warping operation (Equation 2.3) requires a matrix multiplication and two scalar division operations to conform to homogeneous coordinates and is expensive to implement in hardware. Instead, we have modeled this with a second-order polynomial which approximates the inverse homography matrix as follows:

$$x = a_0 + a_1 x' + a_2 y' + a_3 x'^2 + a_4 x' y' + a_5 y'^2$$

$$y = b_0 + b_1 x' + b_2 y' + b_3 x'^2 + b_4 x' y' + b_5 y'^2,$$

(3.1)

where x and y are real-valued source image coordinates and x' and y' are integer-valued coordinates of the rectified image. The coefficients  $a_i$  and  $b_i$  are computed offline.

The integer parts of x and y are used as the index of the source pixel for bilinear interpolation. The fractional parts are used as weights for bilinear interpolation. The values for the image coordinates, x and y, can be obtained by one of the following two approaches:

1. Look-Up Table - The image coordinates can be calculated in *advance* by evaluating the polynomials and storing the results in look-up tables which can be referenced

at run-time. Only one bilinear interpolation for each pixel needs to be carried out at run-time.

2. Real Time Computation - The image coordinates are computed by evaluating the polynomials at run-time and then bilinear interpolation is performed to determine the intensity of each pixel.

For an image that is 640 pixels wide, at least 10 bits are needed to index these pixels. The fractional part is represented by 6 bits bringing the total to a 16-bit representation. The Look-Up Table approach would require 600 KB of memory for storing each of the four coordinates for a total of 2400 KB to rectify both the left and right images. The Stratix S80 FPGA has 9 blocks of 64 KB of on-chip memory for a total of 576 KB. This on-chip memory is insufficient for the size of this problem. The off-chip memory on the TM-4 board can be used but it would require the design of a cache on the FPGA because it is not possible to read a value from the off-chip memory in a single clock cycle. In comparison, real-time computation of the polynomial requires 13 multiplication and 10 addition operations. We have chosen to compute these coordinates in real-time.

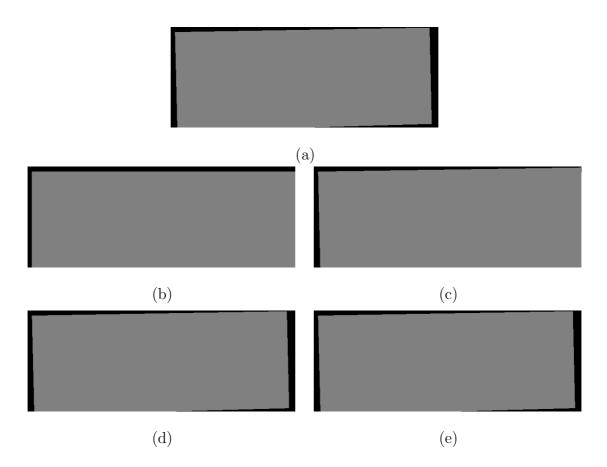

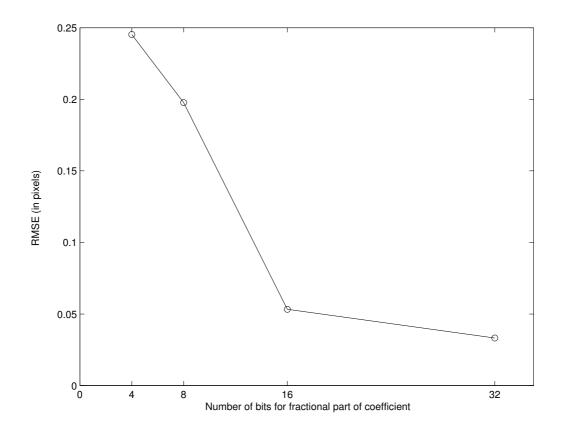

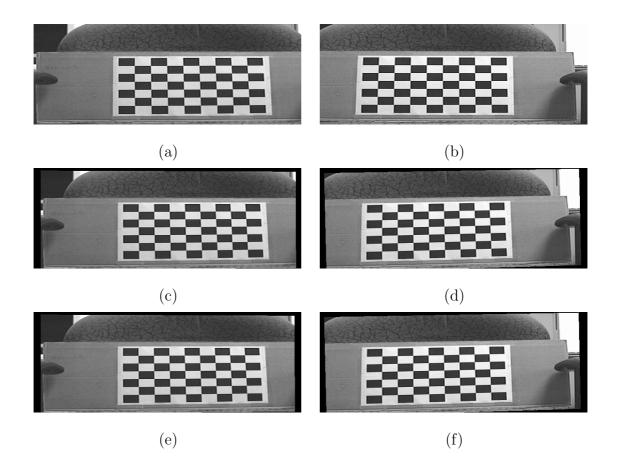

A fixed-point representation is employed for computing Equation 3.1. Figure 3.2 (a) shows the expected orientation of the warped image. The warped image is represented by the gray area. Figure 3.2 (b), (c), (d), and (e) show the resulting warped orientations obtained when the fractional part of the coefficients in Equation 3.1 is represented by 4, 8, 16, and 32 bits respectively. The root-mean-square error (RMSE) based on the resulting orientation is shown in Figure 3.3. There is no significant improvement in the RMSE when representing the coefficients with more than 16 bits so we chose this as the precision for the the coefficients  $a_i$  and  $b_i$ .

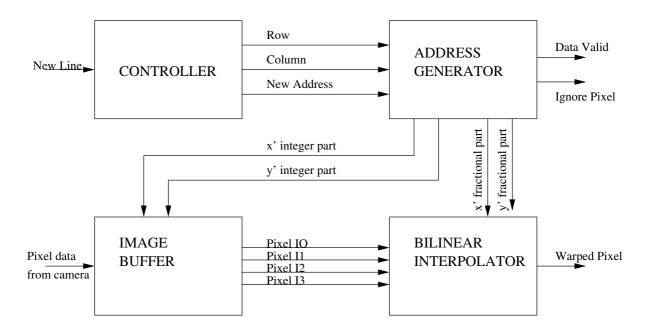

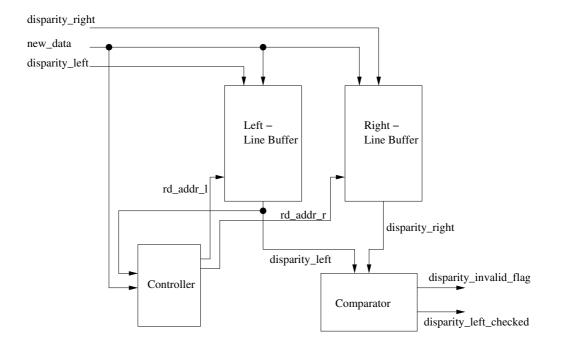

The architecture of the **Image Rectification Unit** is illustrated in Figure 3.4. A stereo-setup with a worst-case vertical misalignment of 16 *scanlines* between the left and right image is assumed, which requires buffering of 32 *scanlines* of both the left and right images. The *Image Buffer* stores the incoming pixels and the *Controller* keeps

Figure 3.2: Comparison of the expected warped image (a) with the resulting warped images when computing Equation 3.1 with 4 (b), 8 (c), 16 (d), and 32 (e) bits of precision for coefficients  $a_i$  and  $b_i$ .

track of the latest source line that arrives into the buffer. If all the lines required for the next output line are available, the *Controller* generates the output indices for pixels in the scanline. The *Address Generator* then computes the source address for the four neighbouring pixels required for bilinear interpolation for each pixel in the scanline. The integer part of the source address is used to read out the required pixels from the buffer. The fractional parts of the source address are used as weights for bilinear interpolation. A warped image is not in general contained in the same region of the image plane as the original image resulting in some "missing" pixels typically at the edges of the warped image. A 1-bit flag is generated to indicate these missing or invalid pixels.

Figure 3.3: Root-mean-square error values for the warped image orientations computed with various precision bits for the coefficients  $a_i$  and  $b_i$ .

Figure 3.4: Architecture of Image Rectification Unit.

Figure 3.5: There is a direct relationship between the epipolar search band and the expected depth of objects in a scene that can be recovered.

# 3.3 Expanding the Disparity Range

A simple and straightforward solution to expanding the disparity range can be achieved by increasing the size of the correlation window to correlate pixels at greater disparities. This increases the size of the *epipolar search band*, which is the area along the image scanline within which a corresponding match is searched for. There is a direct relationship between the search band range and the depth in a scene that can be recovered, as illustrated in Figure 3.5. However, considering that the resource usage on the FPGAs is proportional to the size of the correlation window, it is not an optimal solution because finite device resources pose a restriction.

In addition, in [?] it is shown that the probability of an incorrect stereo match  $P_m^{Total}$  is given by :

$$P_m^{Total} = P_m^a + P_m^b + P_m^c \tag{3.2}$$

where  $P_m^a$  is the probability of mismatching a pair of features when neither feature has its correct match detected in the other image,  $P_m^b$  is the probability of mismatch when one feature has had its correct match detected and  $P_m^c$  is the probability of mismatch when both features have had their correct matches found in the other image.  $P_m^a$ ,  $P_m^b$ and  $P_m^c$  are each proportional to the mean number of candidate matches, and mutually exclusive, and thus  $P_m^{Total}$  is proportional to the epipolar search area considered during matching.

## 3.3.1 The Tracking Correlation Window

We saw above that increasing the size of the correlation window is not a viable solution from either an algorithmic point of view or a hardware implementation point of view. However, in many practical situations, such as when an object gets closer to the cameras, it becomes necessary to be able to handle a larger disparity range.

Fortunately, the input to real-time stereo-vision systems is from cameras that stream images at a rate of 30 fps or higher. At this rate, a large amount of temporal coherence is expected in most real-life image sequences. By modeling and predicting the movement of pixels in an image, we can restrict the epipolar search to a limited area at a particular time frame. The correlation window can shift accordingly along the epipolar line (which for the case of rectified images is the same as a *scanline*) and perform localised correlation rather than performing a blind search over a much larger range, much of which has a very low probability of having the match of interest.

Keeping this in mind, we have modified the original LWPC algorithm to encapsulate the correlation algorithm within a temporal loop. This change is reflected in Step 2 of the LWPC algorithm initially mentioned in Section 2.1.3 as follows:

2. For each scale and orientation, compute local voting functions  $C_{j,s}(x,\tau)$  in a window centred at  $\tau_c$  as

$$C_{j,s}(x,\tau) = \frac{W(x) \otimes [O_l(x)O_r^*(x+\tau_c)]}{\sqrt{W(x) \otimes |O_l(x)|^2}\sqrt{W(x) \otimes |O_r(x)|^2}},$$

(3.3)

where W(x) is a smoothing, localized window and  $\tau_c$  is the pre-shift of the right filter output centred at the disparity of the pixel from the previous frame. This is implemented as the *Primary Tracking Window (PTW)* and its hardware implementation is discussed in Section 3.3.3. The tracking algorithm is currently a very simple one; the window is centred at the estimated disparity from the previous frame for a given pixel. Since images are received at a rate of 30 frames per second or higher, we assume that the disparity of a given pixel will not change drastically from one frame to the next. This allows us to reduce the size of the correlation search area, which results in reduced hardware resources as well as a reduced probability of mismatch assuming we are close to the correct match.

In correlation-based stereo algorithms such as this one the recovered object boundaries tend to be located away from the real ones, a problem known as *boundary over-reach*. Boundary over-reach occurs when the correlation window straddles an object boundary so that part of the window is on an object at one depth and part of it is on an object at another depth. The system in this work also exhibits this phenomenon, but the shiftable nature of the window can be used to overcome this problem in a future version of the system as will be discussed briefly in Section 3.3.5.

## 3.3.2 System Initialisation

When propagating disparity estimates between frames, it is necessary to consider that such algorithms suffer from the risk of getting stuck in a local minima (wrong matches) [?], especially during the initial frames. This problem can be overcome by performing system initialisation using one of the following two methods:

- 1. Coarse-to-fine strategy.

- 2. Stochastic search strategy.

The idea behind a coarse-to-fine strategy is to gradually increase the resolution at which correlation is performed. This performs the initial exhaustive search that is required to give a temporal stereo algorithm a good seed point from which to start. Pro-

#### Chapter 3. Design

cessing the initial few frames at a much coarser scale (say 25% or 50% of their original size) allows the correlation algorithm to search a greater range of disparity in a given time. The main advantage of using a coarse-to-fine strategy is that a valid disparity map is generally available from the first frame. This approach is ideal for a software implementation because it does not increase the computational load. In a hardware implementation though, this approach is less appealing because it requires decision making regarding which scale to use at a specific time, though its potential uses can be considered for a future addition to the system. Furthermore, using results from only a particular scale would mean losing the essence of the LWPC algorithm, which combines results across scales for improved accuracy. This is discussed later in the section.

Stochastic search applies an exhaustive search over a period of time. It normally takes a few frames before complete initialisation of the scene under consideration is achieved. A second correlation window, in addition to the primary window that performs temporal correlation, is required to perform this search. In a software implementation, this means an increase in the computational load. In hardware, the secondary window can operate in parallel with the primary window so that there is no increase in the computation time. We chose to employ this method because this secondary window can also be used after the initialisation stage to help the system recover from mis-matches as discussed below. This is an advantage over the coarse-to-fine strategy. A coarse-to-fine strategy would require frequent reinitialisation and computation of the entire scence at coarser scale to recover from mis-matches whereas the stochastic search approach treats individual pixels separately and is able to recover from a mis-match without switching the computation between coarse and fine scales.

In [?] it is claimed that a coarse-to-fine strategy is preferred over an initialisation stage that uses a window to incrementally search over a wider range, but from our experiments on real image sequences we have found that a secondary correlation window that performs disparity calculations at regularly spaced intervals in successive frames, similar to the initialisation stage employed in [?], gives good results, as will be shown.

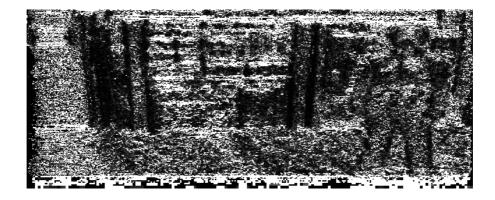

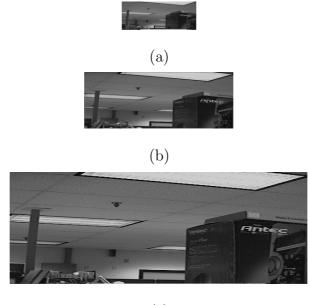

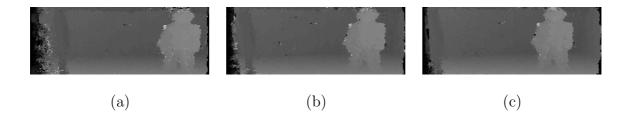

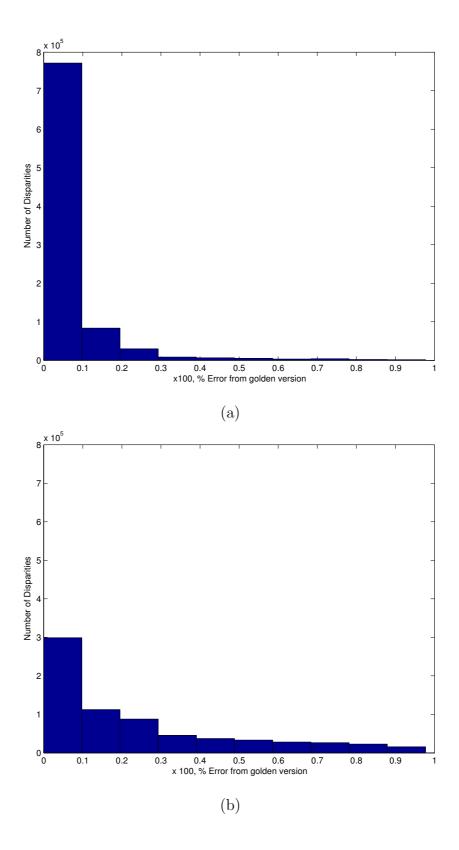

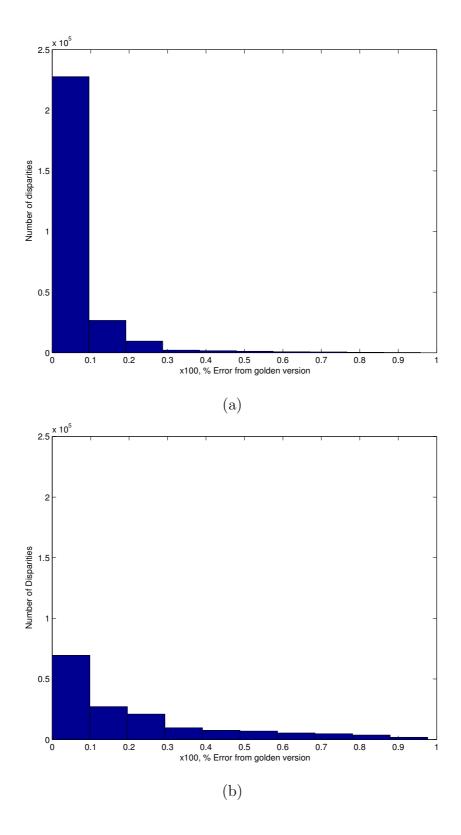

Figure 3.6 shows the results from the initialisation stage for the scene shown in Figure 3.6(a). Figure 3.6 (b) shows the disparity map that the LWPC algorithm would generate if it had no limitations on the maximum disparity. Figure 3.6 (c) to (g) show the settling of the disparity map into the expected disparity of Figure 3.6(b). The Root Mean Square Error (RMSE) between the expected disparity map and the disparity map generated by our modified algorithm steadily decreases at each progressive frames and tends to zero at the fifth frame for this particular scence as shown in Figure 3.6 (h).

We call this second correlation window the Secondary Roving Window (SRW). The main advantage of using this approach is that the SRW also aids in recovery from a mismatch after the initialisation stage. In situations where a new object enters the scene, or a region is dis-occluded, the SRW will pick up this new information, typically within a few frames, and provide a disparity estimate with higher confidence value than the PTW, which can then latch on to this new estimate as illustrated in Figure 3.7. This provides better results as well as much better utilisation of the hardware resources.

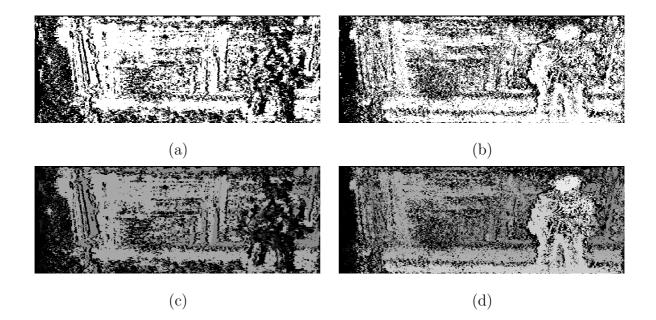

There is a trade-off between the stochastic search area and the time to recovery using this approach. The further that the *SRW* has to search over, the greater number of frames it would require to recover should the *PTW* be stuck at a wrong match. In Figure 3.8 we show the difference in recovery time for the cases when the secondary correlation window is shifted up to a disparity of: i) 140 pixels and ii) 60 pixels. Figure 3.8 (a) shows frame 11 for case (i); the results start to deteriorate as the subject moves to the left and pixels to the right of the subject are dis-occluded. The system completely recovers by frame 15, Figure 3.8 (b). For case (ii), the results deteriorate at frame 12, Figure 3.8 (c), and are already recovered by frame 13, Figure 3.8 (d), though the results get noisier as the maximum disparity of the system increases. When the maximum disparity expected

Figure 3.6: The disparity map at successive time instances are shown in (c) to (g) obtained using our modified temporal algorithm. The expected disparity map is shown in (b) and our modified algorithm reaches this expected disparity by the fifth frame (g) for this particular set-up. The error during the initialisation stage shown in (d) converges to zero.

Figure 3.7: PTW is correctly tracking the peak (denoted by an  $\mathbf{X}$ ) in the confidence measure in (a). In (b), PTW has lost track of the peak, but SRW has picked it up. PTW will latch on to this estimate at the next frame.

Figure 3.8: The recovery time for the system with a maximum secondary shift of 140 pixels is shown in (a) and (b). This can be reduced by using a smaller maximum shift, e.g. 60 pixels as shown in (c) and (d). In the latter case, recovery occurs in one frame as opposed to four.

is known in a particular environment, the roving distance of the SRW can be restricted to minimise the recovery time and noise in the disparity map.

Furthermore, performing disparity calculations at all three scales (1, 2, 4) and in three orientations  $(-45^{\circ}, 0^{\circ}, +45^{\circ})$ , the results of which are summed across scale and orientation, acts as a built-in error-correction feature of the LWPC algorithm. The expected interval between false peaks is approximately the wavelength of the filters applied at each scale. Thus the false peaks at different scales occur at different disparities and summation over the scales yields a prominent peak only at the true disparity [?] as shown in Figure 3.9.

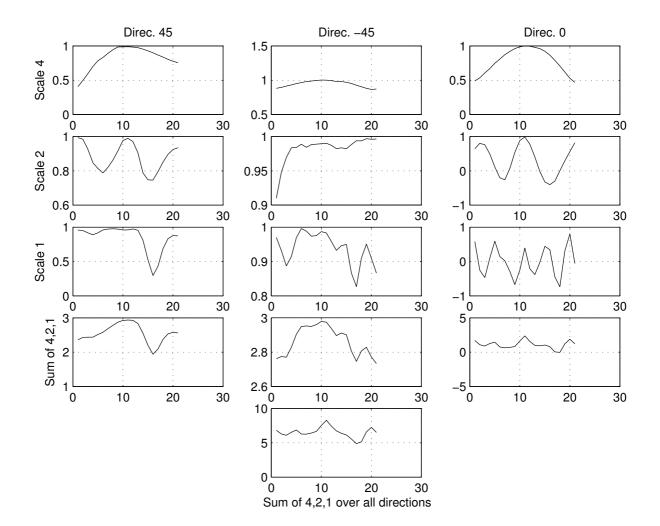

Figure 3.9: LWPC tends to cancel erroneous matches across scales, leaving only the true match after voting. The top three rows show the voting function for three different scales at orientations of  $45^{\circ}$ ,  $-45^{\circ}$ , and  $0^{\circ}$ . The fourth row shows the voting function summed across the scales for each orientation and the final summation across orientations is shown in the fifth row.

## 3.3.3 Comparison of the traditional and new architecture

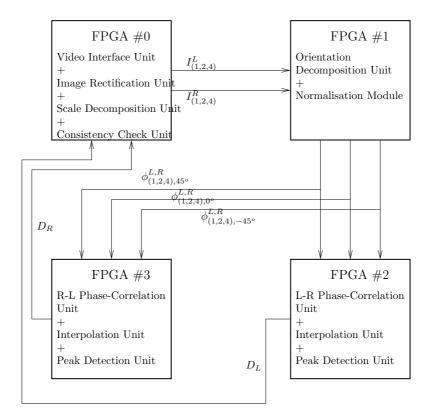

The use of temporal information to seed the correlation windows increases the epipolar search area while keeping the probability of mismatches and the use of hardware logic to a minimum. Nonetheless, it is a challenging task to implement the *shiftable window* correlation in hardware. FPGAs are well suited for processing data in a serial-shift or systolic dataflow fashion. The traditional textbook approach to designing a correlation unit, one which was followed in the the stereo-system on the TM-3 board, follow a

Figure 3.10: Traditional architecture of the correlation unit with fixed window.

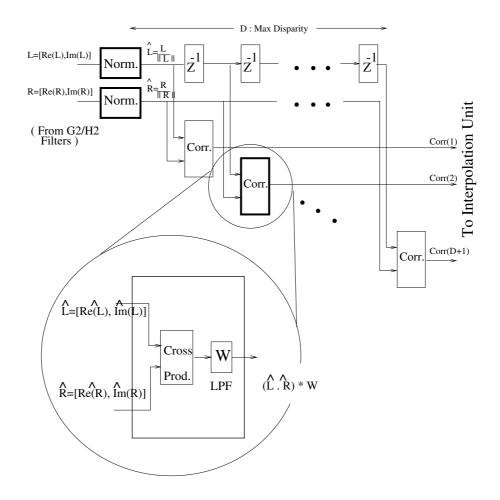

serial-shift dataflow and this only allows for a fixed-window correlation architecture. This architecture, used in [?], is illustrated in Figure 3.10. The correlation,  $W(x) \otimes [O_l(x)O_r^*(x+\tau)]$ , is performed by supplying the left image input of the unit with a new pixel value every cycle and delaying the right image input by 1 to D cycles for each of the D correlation values. For D = 20, this results in a latency of 20 cycles for the first correlation result to appear, after which a new correlation value is generated every cycle.

In the traditional fixed-window correlation architecture the maximum disparity is equal to the actual number of *voting function* / *correlation* blocks used. The resource usage is linearly proportional to the maximum disparity that the correlation unit can support making it prohibitive to use in scenarios with large disparities.

Figure 3.11: Modified correlation unit with two shiftable windows.

To efficiently implement the shiftable window correlation architecture that was discussed previously, we need to take into account the resources available on the specific hardware we intend to use. In the modified correlation algorithm, the data no longer flows in a serial-shift fashion. We do not have *a priori* information on where the window will be located at a particular time instance but we can set the maximum distance over which the correlation might be performed, which we have set to 128 for this work. This requires buffering of partial lines corresponding to the maximum search range.

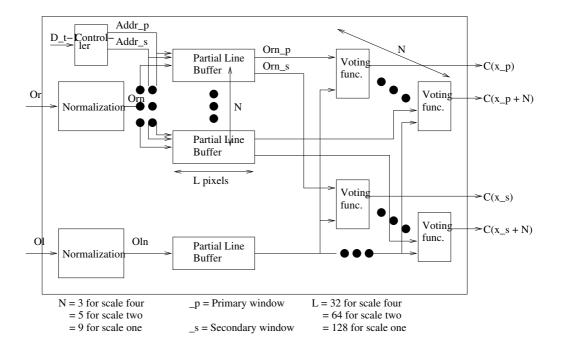

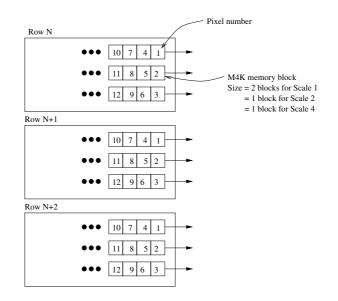

The correlation is carried out at three scales for both the PTW and SRW. We have set the width of the correlation window to 9 pixels at the original scale, requiring nine voting function units. Five voting function units at 50% scale (Scale 2) and three voting function units at 25% scale (Scale 4) are required. We need to buffer n copies of one input, where n corresponds to the number of voting function units at each scale, in order to keep up with the rate of incoming pixels. High-bandwidth M4K memory blocks of the Altera Stratix S80 chip are used to buffer these incoming pixels. In our modified architecture (Figure 3.11), one of the incoming data streams is stored in partial line buffers; the right input stream for a left-to-right correlation and the left input stream for a right-to-left correlation. A left-to-right correlation treats the left input as the reference and the right input is shifted to search for the best match, and viceversa for a right-to-left correlation. The maximum disparity is determined by the size of these buffers whereas the number of voting function units are fixed; 9 for PTW and 9 for SRW. Once all the required pixels for the next correlation operation are available in the buffer, the controller generates an address to read out the required pixel for the current correlation window. To minimize the resource usage on the FPGA, the partial line buffers are implemented using true dual-port memories so that two pixel values can be independently read from the buffer each cycle, one for each of the correlation windows.

The *SRW* centres at a disparity of 9 for the first frame, and shifts in increments of L = 9, the correlation window length, for the successive frames until it reaches a disparity value of 128, or some other user-specified maximum. At the next frame, the window centres at 0 disparity, after which it circles back to being centred at 9 and the cycle continues. The effective range of disparity that our system can handle is 128 pixels but this can easily be increased to accommodate larger disparity. There is a tradeoff between the time to recovery from a mismatch and the maximum disparity that the system can handle, as discussed earlier. For a maximum disparity of 128 pixels with increments of 9 pixels per frame for the *SRW*, the worst-case time to recovery is 433 milliseconds corresponding to a wait of 13 frames.

A comparison of the relative resource requirements for a traditional architecture against our modified architecture is shown in Table 3.1. These are calculated for performing the correlation in three orientations at three scales. The number of *normalisation units* remains the same in both architectures. The number of *voting function units*, the core of the correlation module, required for the modified architecture is actually less than that required for a traditional architecture (102 v.s. 105) for a significantly larger

|                     | # of      | Altera      | On-chip | 9-bit    |

|---------------------|-----------|-------------|---------|----------|

| $\mathbf{Unit}$     | Blocks    | LEs         | M4K     | DSP      |